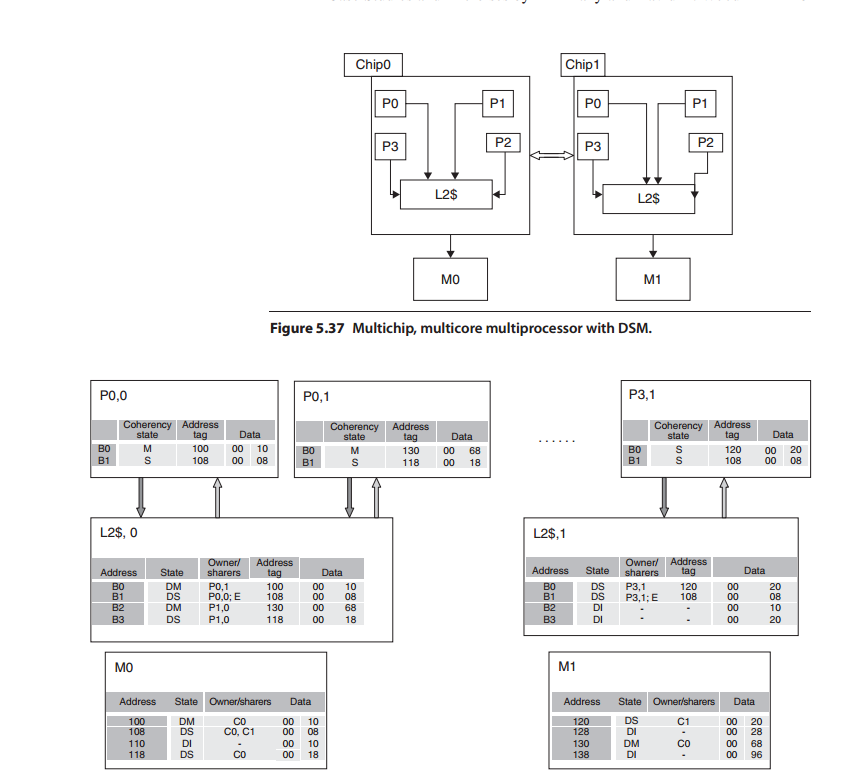

Question: For each part of this exercise, assume the initial cache and memory state in Figure 5.38. Each part of this exercise specifies a sequence of

For each part of this exercise, assume the initial cache and memory state in Figure 5.38. Each part of this exercise specifies a sequence of one or more CPU operations of the form:

P#:

where P# designates the CPU (e.g., P0,0), is the CPU operation (e.g., read or write),

denotes the memory address, and indicates the new word to be assigned on a write operation. What is the final state (i.e., coherence state, sharers/owners, tags, and data) of the caches and memory after the given sequence of CPU operations has completed? Also, what value is returned by each read operation?a. P0,0: read 100

b. P0,0: read 128

c. P0,0: write 128

d. P0,0: read 120

e. P0,0: read 120 P1,0: read 120

f. P0,0: read 120 P1,0: write 120

g. P0,0: write 120

h. P0,0: write 120

Step by Step Solution

There are 3 Steps involved in it

To determine the final state of the caches and memory after each operation you need to understand th... View full answer

Get step-by-step solutions from verified subject matter experts